# PHYTIUM飞腾

# FT-1500A/4 高性能通用微处理器 数据手册

(V1.8)

天津飞腾信息技术有限公司 二零一九年五月

## 版本历史

以下为此文档释放过的更新版本

| 日期         | 版本号   | 作者    | 更新说明                         |  |

|------------|-------|-------|------------------------------|--|

| 2014.10.20 | 1.0   | 技术支持部 | 初版                           |  |

| 2014.12.26 | 1.1   | 技术支持部 | 调整文档结构                       |  |

| 2015.04.27 | 1.2   | 技术支持部 | 调整文档结构                       |  |

| 2015.09.06 | 1.3   | 技术支持部 | 更新上电时序                       |  |

| 2015.12.19 | 1.3.1 | 技术支持部 | 调整上电时序                       |  |

| 2016.03.12 | 1.4   | 技术支持部 | 增加 GPIO 复用列表和装焊温度曲线等内容;调整    |  |

| 2010.03.12 | 1.4   | 双小又行印 | 了文档结构及部分内容                   |  |

| 2016.07.05 | 1.5   | 技术支持部 | 调整文档结构                       |  |

| 2018.2.07  | 1.6   | 技术支持部 | 调整文档结构;增加 FCR 寄存器说明;完善 spi 寄 |  |

| 2018.2.07  | 1.0   | 双小又行前 | 存器配置寄存器列表。                   |  |

| 2018.06.05 | 1.7   | 技术支持部 | 完善 spi 寄存器配置寄存器列表;完善电气特性     |  |

| 2019.05.09 | 1.8   | 技术支持部 | 新增芯片介绍;完善 LPC 说明;调整文档结构      |  |

技术支持邮箱: support@phytium.com.cn

# 版权所有© 天津飞腾信息技术有限公司 2019。

此文档用于指导用户的相关应用和开发工作。天津飞腾信息技术有限公司对此 文档内容拥有版权,并受法律保护。

# 目 录

| 1 | 芯片   | 介绍                              | 1  |

|---|------|---------------------------------|----|

| 2 | 技术   | ₹指标                             | 1  |

| 3 | 功能   | b描述                             | 2  |

| 4 | CPU  | 」接口                             | 2  |

|   | 4.1  | 地址空间分配                          | 2  |

|   |      | 4.1.1 PCIE 配置、IO 和 MEM32 地址空间划分 | 3  |

|   |      | 4.1.2 MIO 地址空间                  |    |

|   |      | 4.1.3 GMAC 控制器地址空间              | 3  |

|   | 4.2  | DDR 接口                          | 4  |

|   | 4.3  | PCIE 接口                         |    |

|   |      | 4.3.1 寄存器说明                     |    |

|   |      | GMAC 接口                         |    |

|   | 4.5  | LPC 接口                          |    |

|   |      | 4.5.1 寄存器说明                     |    |

|   | 4.6  | SPI 接口                          | 8  |

|   |      | 4.6.1 寄存器说明                     |    |

|   | 4.7  | UART 接口                         | 12 |

|   |      | 4.7.1 寄存器说明                     |    |

|   | 4.8  | I2C 接口                          |    |

|   |      | 4.8.1 寄存器说明                     | 25 |

|   | 4.9  | GPIO 接口                         | 40 |

|   |      | 4.9.1 GPIO 复用说明                 | 40 |

|   | 4    | 4.9.2 GPIO 寄存器说明                | 42 |

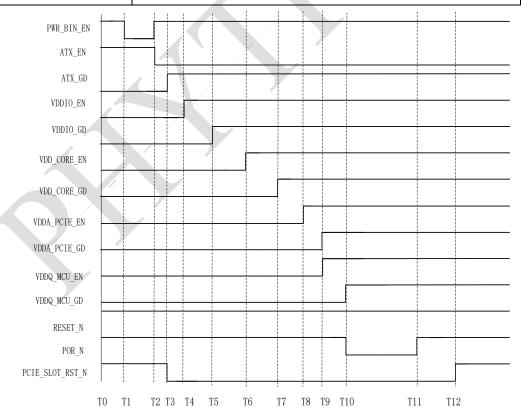

|   | 4.10 | )上电时序                           | 44 |

| 5 | 电气   | 〔特性                             | 47 |

|   | 5.1  | 极限工作条件                          | 47 |

|   | 5.2  | 典型工作参数                          | 47 |

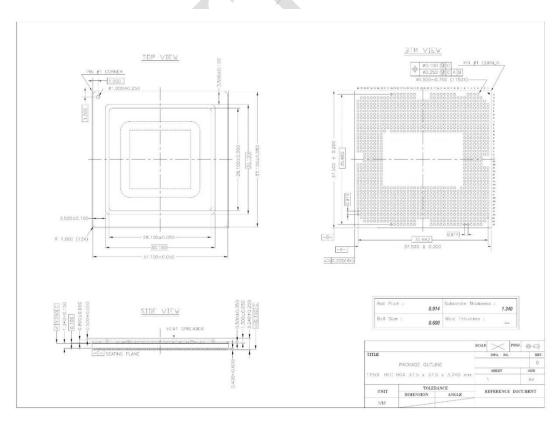

| 6 | 封装   | き数据                             | 48 |

|   | 6.1  | 封装尺寸                            | 48 |

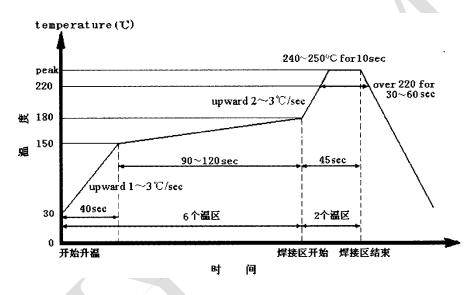

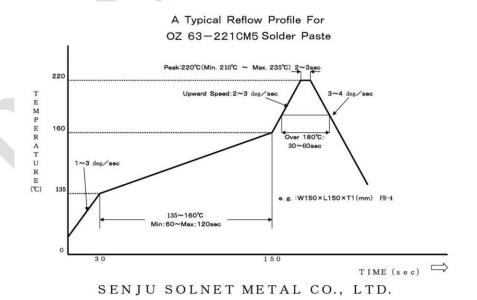

| 7 | 装焊   | 旱温度曲线                           | 49 |

|   | 7.1  | 无铅焊接温度曲线中各温区的作用                 | 49 |

|   | 7.2  | 有铅焊接温度曲线中各温区的作用                 | 50 |

| 8 | 引胠   | 甲描述                             | 51 |

#### FT-1500A/4 数据手册

| 8.1 | 通用 IO 类引脚(118 PIN) | 51 |

|-----|--------------------|----|

| 8.2 | GMAC 引脚(28 PIN)    | 57 |

| 8.3 | PCIE 引脚(140 PIN)   | 58 |

| 8.4 | DDR3 引脚(312 PIN)   | 62 |

| 8.5 | 电源引脚(552 PIN)      | 72 |

### 1 芯片介绍

FT-1500A 系列 4 核处理器芯片(FT-1500A/4)集成 4 个自主开发的 ARMv8 指令集兼容处理器内核 FTC660,采用片上并行系统(PSoC)体系结构,主要面向各类桌面终端、便携式终端和轻量级服务器等应用领域,满足通用信息系统中的网络服务、邮件服务、存储服务、办公、上网、文字处理、图形图像处理、音视频处理等业务需求。

### 2 技术指标

主要技术指标如下:

- ARM V8 架构,支持 ARM64 指令集

- 集成 4 个 FTC660 处理器核

- 核心时钟频率 1.5GHz (标配)

- L1 数据 Cache 32KB

- L2 Cache 8MB

- L3 Cache 8MB

- 峰值性能 24GFlops@1.5GHz

- 典型功耗 15W

- 核电压 0.9V

- 集成 2 个 64 位总线 DDR3 存储控制器,速率可达 1600Mbps,访存带宽可达 25.6GB/s

- 集成 32 Lane PCI Express v3.0 接口,最多支持 4 个 PCIE root complex,不能作为 endpoint 使用

- BGA1150 封装, 0.914mm 球间距, 封装尺寸 37.5mmX37.5mm

- IO 电压 1.8V,包括 UART、I2C、GMII、GPIOA、GPIOB、GPIOC、GPIOD、LPC

- 支持电源关断、时钟关断、DVFS

- 支持商业、工业等分级,温度范围为标准的商业温度范围(0°C~65°C)和工业级温度范围(-40°C~+85°C)

# 3 功能描述

表 3-1 功能描述

| 硬件特性  |                                         | 说明                                                        |  |  |

|-------|-----------------------------------------|-----------------------------------------------------------|--|--|

| Core  | 兼容 ARM V8 指令集<br>的 FTC660 核<br>(FTC660) | 4 个,典型工作频率 1.5GHz。支持电源关断                                  |  |  |

| 存储控制器 | DDR3 SDRAM 控制器                          | 2 个控制器,支持带 ECC 的 DDR3 DIMM,支持 RDIMM、<br>UDIMM、SODIMM、表贴颗粒 |  |  |

|       | PCIE3.0 RootComplex                     | 2个x16,每个x16可分拆为2个x8,独立控制                                  |  |  |

|       | 千兆以太网控制器                                | 1 个控制器,均支持 1000M/100M/10M 自适应,物理接口                        |  |  |

|       | 12以从州江南部                                | 支持 MII、GMII 规范,电压 1.8V                                    |  |  |

|       | Flash 控制器                               | 1个 SPI 接口的 Flash 控制器,支持 4个片选,单片最大支                        |  |  |

|       | Flasii 红刺鱼                              | 持容量为 512MB, 电压 1.8V                                       |  |  |

| 外设    | UART                                    | 2个 UART, 其中 UART0 为 9 线全功能串口, UART1 为 3                   |  |  |

| 外以    | UAKI                                    | 线调试串口, 电压 1.8V, 调试串口默认使用 UART1                            |  |  |

|       | I2C                                     | 2个 I2C Master 控制器,电压 1.8V                                 |  |  |

|       | GPIO                                    | 4 个 8 位 GPIO 接口, GPIOA[0:7], GPIOB[0:7],                  |  |  |

|       | GFIO                                    | GPIOC[0:7],GPIOD[0:7],电压 1.8V                             |  |  |

|       | LPC                                     | 1 个 LPC 接口,兼容 Intel Low Pin Count 协议,可接 SuperIO           |  |  |

|       | LFC                                     | 等外围芯片, 电压 1.8V                                            |  |  |

|       | 内核电源                                    | 0.9V                                                      |  |  |

| 电源    | 存控电源                                    | 1.5V                                                      |  |  |

|       | IO 电源                                   | 1.8V                                                      |  |  |

# 4 CPU接口

### 4.1 地址空间分配

全局寄存器地址空间分配如下:

表 4-1 系统地址空间

| 地址空间                         | 设备           |  |  |

|------------------------------|--------------|--|--|

| 0x000_00000000~0x000_1FFFFFF | SPI,预留 512MB |  |  |

| 0x000_20000000~0x000_27FFFFF | LPC,预留 128MB |  |  |

|                               | 预留 128MB,包括 MIO(uart/i2c/wdt/gpio),cru, |  |  |

|-------------------------------|-----------------------------------------|--|--|

| 0x000_28000000~0x000_2FFFFFFF | Error, icu, MCU0、MCU1、pcie 控制寄存器, PMA   |  |  |

|                               | 配置寄存器,gmac, pmc, mmu, gpv 等             |  |  |

| 0-000 20000000 0-000 2000000  | DTI, 预留 160MB(现在 32MB+4MB)包括 generic    |  |  |

| 0x000_30000000~0x000_39FFFFFF | Timer、0x000_300000000 是 ROMTable 基址     |  |  |

| 0x000_3A000000~0x000_3AFFFFFF | MN,16MB                                 |  |  |

| 0x000_40000000~0x000_7FFFFFF  | PCIE 的配置、IO 和 MEM32 空间,1GB              |  |  |

### 4.1.1 PCIE 配置、IO 和 MEM32 地址空间划分

表 4-2 PCIE 配置、IO、MEM32 地址空间划分

| 地址范围                           | 大小    | 用途       |

|--------------------------------|-------|----------|

| 0x000_40000000~0x000_4FFFFFFF  | 256MB | 配置空间     |

| 0x000_500000000~0x000_5FFFFFFF | 256MB | IO 空间    |

| 0x000_60000000~0x000_7FFFFFFF  | 512MB | MEM32 空间 |

### 4.1.2 MIO 地址空间

表 4-3 MIO 内部空间划分

| 起始地址空间     | 设备名   | 说明                   |

|------------|-------|----------------------|

| 0x00000000 | UART0 | 9 针全线制串口             |

| 0x00001000 | UART1 | 3线制串口                |

| 0x00002000 | I2C0  | 既可做 Master 也可做 Slave |

| 0x00003000 | I2C1  | 既可做 Master 也可做 Slave |

| 0x00004000 | WDT0  | 看门狗                  |

| 0x00005000 | WDT1  | 看门狗                  |

| 0x00006000 | GPIO  | 4个8位接口,最多32位         |

| 其它         | 保留    |                      |

### 4.1.3 GMAC 控制器地址空间

表 4-4 GMAC 控制器地址空间划分

GMAC 控制器 0 基地址: 0x28c00000 GMAC 控制器 1 基地址: 0x28c02000

| 地址偏移          | 大小  | 描述         |  |

|---------------|-----|------------|--|

| 0x0000~0x0FFF | 4KB | GMAC 寄存器空间 |  |

| 0x1000~0x1FFF | 4KB | GMAC DMA 寄存器空间 |

|---------------|-----|----------------|

|---------------|-----|----------------|

#### 4.2 DDR 接口

DDR 接口支持 X8 和、X4 以及 x16 两三种 DDR 颗粒类型, 如表 4-5 所示。 DDR 接口支持 1.5V DDR3 的 RDIMM、UDIMM、SODIMM 等内存条类型。

颗粒芯片位宽

颗粒芯片数目

X16

4

X8

8

X4

16

注:该表芯片数目中,不包含 ECC 内存颗粒

表 4-5 DDR 接口支持的内存形式

#### 4.3 PCIE 接口

PCIE 接口支持 PCIE3.0 规范,兼容 PCIE2.0、PCIE1.0 规范,其特点如下:

- 包含 2 个 x16 root complex 接口, PCIE 0 和 PCIE 1;

- 每个 X16 最多拆分为 2 个 root, 也就是说每个 X16 的拆分模式可以为 1 个 X16 或者 2 个 X8;

- 可支持 X1, X2, X4, X8 支持翻转 (逆序);

- PCIE 翻转兼容说明;

若是 PCIE0[0:7]、PCIE1[0:7]翻转(逆序)后连接 PCIE 插槽,则只支持 X8 外设。而 PCIE0[8:15]、PCIE1[8:15]则不受此约束限制,用户可根据需要进行配置。

#### 4.3.1 寄存器说明

#### 4.3.1.1 基地址

表 4-6 PCIE 基地址

| 名称   | 基地址         |  |

|------|-------------|--|

| PCIE | 0x2810_0000 |  |

#### 4.3.1.2 寄存器列表

表 4-7 寄存器描述

| 偏移地址   | 名称                      | 读写方式 | 说明        |

|--------|-------------------------|------|-----------|

| 0x0E00 | REG_PEU_BIF_MODE        | R/W  | 拆分模式寄存器   |

| 0x0E08 | REG_PEU_TX_LANE_FLIP_EN | R/W  | 链路反转设置寄存器 |

### 4.3.1.2.1 拆分模式寄存器(0x0E00)

表 4-8 拆分模式寄存器

| 位     | 名称             | 读写方式 | 默认值 | 说明                                            |

|-------|----------------|------|-----|-----------------------------------------------|

| [3:2] | PCIE1_bif_mode | R/W  | 0x1 | PCIE 1 的分拆模式设置: •00-全部关闭 •01-一个 16x •10-两个 8x |

| [1:0] | PCIE0_bif_mode | R/W  | 0x1 | PCIE 0 的分拆模式设置: •00-全部关闭 •01-一个 16x •10-两个 8x |

# 4.3.1.2.2 链路反转设置寄存器(0x0E08)

表 4-9 链路反转设置寄存器

| 位    | 名称                       | 读写方式 | 默认值 | 说明                  |

|------|--------------------------|------|-----|---------------------|

| [15] | pcie1_c3_tx_lane_flip_en | R/W  | 0x0 |                     |

| [14] | pcie1_c2_tx_lane_flip_en | R/W  | 0x0 |                     |

| [13] | pcie1_c1_tx_lane_flip_en | R/W  | 0x0 |                     |

| [12] | pcie1_c0_tx_lane_flip_en | R/W  | 0x0 |                     |

| [11] | pcie1_c3_rx_lane_flip_en | R/W  | 0x0 |                     |

| [10] | pcie1_c2_rx_lane_flip_en | R/W  | 0x0 |                     |

| [9]  | pcie1_c1_rx_lane_flip_en | R/W  | 0x0 | 为 1 表示手动设置 lane 反转  |

| [8]  | pciel_c0_rx_lane_flip_en | R/W  | 0x0 | 为 I 农小于幼以且 Ialle 及拉 |

| [7]  | pcie0_c3_tx_lane_flip_en | R/W  | 0x0 |                     |

| [6]  | pcie0_c2_tx_lane_flip_en | R/W  | 0x0 |                     |

| [5]  | pcie0_c1_tx_lane_flip_en | R/W  | 0x0 |                     |

| [4]  | pcie0_c0_tx_lane_flip_en | R/W  | 0x0 |                     |

| [3]  | pcie0_c3_rx_lane_flip_en | R/W  | 0x0 |                     |

| [2]  | pcie0_c2_rx_lane_flip_en | R/W  | 0x0 |                     |

| [1] | pcie0_c1_rx_lane_flip_en | R/W | 0x0 |

|-----|--------------------------|-----|-----|

| [0] | pcie0_c0_rx_lane_flip_en | R/W | 0x0 |

#### 4.4 GMAC 接口

以太网控制器(GMAC)的主要功能是在兼容 IEEE802.3-2005 标准的以太 网中发送和接收数据,支持 GMII 和 MII 的 PHY 接口。

#### GMAC 接口特点:

- 支持速率 1000Mbps/100Mbps/10Mbps

- 支持 IEEE 802.3-2005 Ethernet MAC, Gigabit Media Independent Interface (GMII) / Media Independent Interface (MII)

芯片包含一路 GMAC 接口, GMAC 接口信号主要分三类: 时钟接口、数据接口和管理接口。接口信号列表见 GMAC 引脚。

#### 外围接口的需求:

- CPU 的 OSC CLK 125MHz 时钟, 需外部提供。

- GMU CLK OSC、G1 CLK TX 和G1 CLK RX在不使用情况下接地。

- 如果没有使用 GMAC,建议 125MHz 外部时钟输入引脚 GMAC\_OSC 接地。

- 时钟需求: GMAC 控制器有 1 个外部时钟输入引脚 GMU\_CLK\_OSC, 频率为 125MHz, 需外部提供。

- 外围接口电路与下列引脚连接的信号线,有等长需求,如表 4-10 所示,每个分组内各信号线要求等长。数据信号比时钟信号长 0~0.2ns,下表中每组的首个信号为该组的时钟信号,其它为数据信号。

| 组       | 1          | 2         | 3       |

|---------|------------|-----------|---------|

|         | G1_CLK_GTX | G1_CLK_RX | G1_MDIO |

|         | G1_TX0~7   | G1_COL    | G1_MDC  |

| I/O PAD | G1_TXEN    | G1_CRS    |         |

| I/OTAD  | G1_TXER    | G1_RX0~7  |         |

|         |            | G1_RXDV   |         |

|         |            | G1_RXER   |         |

表 4-10 GMAC

#### 4.5 LPC 接口

LPC (Low Pin Count) 主要用来连接鼠标、键盘、串口、低速 Flash 等设备。 LPC 接口采用 1.8V 的 LVCMOS,因而在连接 LPC 设备时需要进行电平转换。 芯片集成了一个 LPC 控制器, LPC 接口建议通过 CPLD/FPGA, 进行电平的转换

LPC 的时钟信号为 GPIOD2\_EXT\_LPC\_LCK, 时钟频率为 33MHz, 必须由外部提供。CPU 中的 LPC 控制器只支持 4 字节对齐地址的访问, 如果使用单字节访问, 就会造成部分地址无法使用, 因此建议使用 4 字节访问,详情请参考《FT-1500A 平台 LPC 兼容规范》。

#### 4.5.1 寄存器说明

#### 4.5.1.1 基地址

表 4-11 LPC 基地址

| 名称  | 基地址         |

|-----|-------------|

| LPC | 0x27FF_0000 |

#### 4.5.1.2 寄存器列表

表 4-12 LPC 寄存器说明

| 偏移地址   | 名称        | 读写方式 | 默认值           | 含义                      |

|--------|-----------|------|---------------|-------------------------|

| 0 EEE0 | 串行中断配置    | D/W  | 221 0000 0000 | 设置 LPC 接口数据读取使能、起始周期、串行 |

| 0xFFE8 | 寄存器[31:0] | R/W  | 32'h8000_0000 | 中断模式和支持设备数量。            |

注:操作 LPC 的寄存时,请确保 LPC 的外部电路连接正常,否则读写 LPC 寄存器会失败。

### 4.5.1.2.1 串行中断配置寄存器(0xFFE8)

表 4-13 串行中断配置寄存器

| 地址          | 名称             | 读写方式   | 默认值         | 含义              |

|-------------|----------------|--------|-------------|-----------------|

| 0x27FF_FFFC | lpc addr cfg   | R/W    | 8'b11100100 | 配置APB接口地址的设备    |

| 0x2/11_1110 | reg[7:0]       | IX/ VV | 8 011100100 | 类型              |

| 027EE EEE9  | lpc long wait  | D/W    | 32'h0       | 长等待超时控制寄存器      |

| 0x27FF_FFF8 | ctrl req[31:0] | K/W    | 32 110      | <b>人寺付妲門</b>    |

|             | 1              |        | 32'h0       | 中断状态 (串行中       |

| 0x27FF_FFF4 | lpc int status | RO     |             | 断)bit29~0:串行中断, |

|             | reg[31:0]      |        |             | bit30DMA请求中断    |

| 0x27FF_FFF0 | lpc int clear  | R/W    | 32'h0       | 清除中断寄存器         |

|                                         | reg[31:0]                    |     |                   |                                                                                                                                                                                                                    |

|-----------------------------------------|------------------------------|-----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x27FF_FFEC lpc msg length cfg reg[3:0] |                              | R/W |                   | firmware memory类型的<br>报文长度配置寄存器(暂<br>未使用)                                                                                                                                                                          |

| 0x27FF_FFE8                             | nu_serirq_confi<br>g[31:0]   | R/W | 32'h8000_00<br>00 | 配置寄存器(bit31: 针对<br>读数据每次读4 bytes数据<br>使能标志(1'b1: 读<br>1byte); bit1~0:起始周<br>期配置(2'b11: 8;<br>2'b10:6; 否则4, 默认4<br>clk), bit2: 串行中断模<br>式配置默认连续模式 默<br>认为连续模式),<br>bit3~4: 支持的串行中断<br>设备数量(2'b01 代表<br>32 否则16默认16) |

| 0x27FF_FFE4                             | lpc err status reg[2:0]      | RO  | 3'h0              | 错误状态寄存器,记录最近一次发生错误的状态。3'b000:无效3'b010:长等待超时3'b001:短等待超时3'b100:SYNC error3'b110:非法的读写操作                                                                                                                             |

| 0x27FF_FFE0                             | lpc firmware id sel reg[2:0] | R/W | 4'h0              | firmware memory设备ID<br>选择配置寄存器<br>3'b001 22: 19作为ID<br>3'b010 23: 20作为ID<br>3'b011 24: 21作为ID<br>默认30: 27作为ID                                                                                                      |

| 0x27FF_FFDC                             | lpc DMA ID<br>cfg reg[2:0]   | R/W | 3'h6              | DMA 设备ID配置寄存器                                                                                                                                                                                                      |

# 4.6 SPI 接口

SPI 接口仅支持连接用于存储 BIOS 用的 FLASH 芯片。

### 4.6.1 寄存器说明

### 4.6.1.1 基地址

表 4-14 SPI 基地址

| 名称  | 基地址         |

|-----|-------------|

| SPI | 0x1FFF_FF00 |

### 4.6.1.2 寄存器列表

表 4-15 寄存器列表

| 地址   | 寄存器名          | 说明                            |  |  |

|------|---------------|-------------------------------|--|--|

| 0x00 | 配置寄存器         | 配置访问数据空间时产生的读写命令、SCK 分频等信息    |  |  |

| 0x14 | Flash 容量设置寄存器 | 设置所连接的 FLASH 容量,每个片选所接容量必须相同  |  |  |

| 0x18 | 写缓冲 flush 寄存器 | 写 1 将把写缓冲中的数据 flush 到 FLASH   |  |  |

| 0x20 | 命令端口寄存器       | 通过端口方式访问 SPI 时设置的命令           |  |  |

| 0x24 | 地址端口寄存器       | 通过端口方式访问 SPI 时设置的地址           |  |  |

| 0x28 | 高位数据寄存器       | 通过端口方式访问 SPI 时的高 4 字节数据       |  |  |

| 0x2C | 低位数据寄存器       | 通过端口方式访问 SPI 时的低 4 字节数据,读写将触发 |  |  |

|      | N   上 XX      | SPI 总线操作                      |  |  |

# 4.6.1.2.1 配置寄存器 (0x00)

表 4-16 配置寄存器

| 位     | 名称        | 读写方式 | 默认<br>值 | 说明                                                                                                                                     |

|-------|-----------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------|

| [7:6] | cmd_mode  | R/W  | 0x0     | 设置读写数据空间时所发出的 SPI 命令  •00-发 read(03)和 pp(02);  •01-发 4read(13)和 4pp(12);  •10-发 fast_read(0b)和 pp(02);  •11-发 4fast_read(0c)和 4pp(12); |

| [5]   | addr_mode | R/W  | 0x0     | 设置发出 read、fast_read 和 pp 命令时的地址模式                                                                                                      |

|       |          |         |      | 设置发出 fast_read 和 4fast_read 时是否发 dummy 字节  |

|-------|----------|---------|------|--------------------------------------------|

| [4]   | dummy    | R/W     | 0x0  | •0-不发;                                     |

|       |          |         |      | •1-发;                                      |

| [2]   | www.modo | D/W     | 0**0 | •0-每次写请求直接发编程命令;                           |

| [3]   | wr_mode  | R/W 0x0 |      | •1-写数据先放入缓冲,多次写合并编程;                       |

| [2:0] | sck_sel  | R/W     | 0x0  | •000-如果定义了 SPEEDSIM_FLASH, sck 为输入时钟 clk 的 |

|       |          |         |      | 2 分频, 否则为 16 分频;                           |

|       |          |         |      | •001-sck 为 pclk 的 2 分频;                    |

|       |          |         |      | •010-sck 为 pclk 的 4 分频;                    |

|       |          |         |      | •011-sck 为 pclk 的 8 分频;                    |

|       |          |         |      | •100-sck 为 pclk 的 16 分频;                   |

|       |          |         |      | •101-sck 为 pclk 的 32 分频;                   |

|       |          |         |      | •110-sck 为 pclk 的 64 分频;                   |

|       |          |         |      | •111-sck 为 pclk 的 128 分频。                  |

## 4.6.1.2.2 容量寄存器 (0x14)

表 4-17 容量寄存器

| 位     | 名称             | 读写方式 | 默认值 | 说明       |

|-------|----------------|------|-----|----------|

|       |                |      |     | •0–16MB  |

|       |                |      |     | •1–32MB  |

|       |                |      |     | •2–64MB  |

| [2,0] | flesh samesity | R/W  | 0x0 | •3–128MB |

| [2:0] | flash_capacity | R/W  | UXU | •4–256MB |

|       |                |      |     | •5–512MB |

|       | 7              |      |     | •6–1GB   |

|       |                |      |     | •7-非法值   |

## 4.6.1.2.3 写缓冲寄存器 (0x18)

表 4-18 写缓冲寄存器

|   | 位   | 名称    | 读写方式 | 默认值 | 说明               |

|---|-----|-------|------|-----|------------------|

| Ī | [0] | flush | R/W  | 0x0 | 写 1 将产生 flush 操作 |

### 4.6.1.2.4 命令端口寄存器 (0x20)

表 4-19 命令端口寄存器

| 位       | 名称         | 读写方式 | 默认值 | 说明                   |

|---------|------------|------|-----|----------------------|

| [17:16] | flash_sel  | R/W  | 0x0 | 选择要操作的 flash         |

| [15:8]  | command    | R/W  | 0x0 | 要发出的 SPI 命令          |

| [7]     | reserved   | R/W  | 0x0 | 保留                   |

|         |            |      |     | 是否带地址                |

| [6]     | addr_mode0 | R/W  | 0x0 | •0-不带地址              |

|         |            |      |     | •1-带地址               |

|         |            |      |     | 地址模式                 |

| [5]     | addr_mode1 | R/W  | 0x0 | •0-3 字节地址            |

|         |            |      |     | •1-4 字节地址            |

|         |            |      |     | 是否发 dummy 字节         |

| [4]     | dummy      | R/W  | 0x0 | •0-不发                |

|         |            |      |     | •1-发                 |

| [3:0]   | R/W_num    | R/W  | 0x0 | 读写字节数目,有效值为0,1,2,4,8 |

## 4.6.1.2.5 地址端口寄存器 (0x24)

表 4-20 地址端口寄存器

| 位      | 名称   | 读写方式 | 默认<br>值 | 说明 |

|--------|------|------|---------|----|

| [31:0] | addr | R/W  | 0x0     | 地址 |

### 4.6.1.2.6 高位寄存器 (0x28)

表 4-21 高位寄存器

| 位      | 名称   | 读写方式 | 默认<br>值 | 说明     |

|--------|------|------|---------|--------|

| [31:0] | data | R/W  | 0x0     | 高4字节数据 |

#### 4.6.1.2.7 低位寄存器 (0x2C)

表 4-22 低位寄存器

| 位      | 名称   | 读写方式 | 默认<br>值 | 说明     |

|--------|------|------|---------|--------|

| [31:0] | data | R/W  | 0x0     | 低4字节数据 |

### 4.7 UART 接口

UART (Universal Asynchronous Receiver/Transmitter),通用异步接收/发送装置,定义了一种并行数据与串行数据进行转换的协议。芯片中包含 1 个 9 线接口 UART0 和 1 个 3 线制接口 UART1,兼容 16550 标准。

#### 4.7.1 寄存器说明

#### 4.7.1.1 基地址

表 4-23 UART 基地址

| 名称    | 基地址         |  |

|-------|-------------|--|

| UART0 | 0x2800_0000 |  |

| UART1 | 0x2800_1000 |  |

### 4.7.1.2 寄存器列表

表 4-24 UART 寄存器说明

| 偏移地址 | 名称  | 读写方式    | 默认值  | 说明             |

|------|-----|---------|------|----------------|

| 000  | DDD | D.O.    | 00   | 接收缓存寄存器        |

| 0x00 | RBR | RO      | 0x0  | LCR[7] bit = 0 |

|      | THD | WO      | 00   | 发送保持寄存器        |

|      | THR | WO      | 0x0  | LCR[7] bit = 0 |

|      | DLL | R/W 0x0 | 0x0  | 波特率除数低位字节      |

|      | DLL | R/W     | UXU  | LCR[7] bit = 1 |

| 0x04 | DLH | R/W 0x0 | 0x0  | 波特率除数高位字节      |

| 0x04 | DLN | K/ W    | UXU  | LCR[7] bit = 1 |

|      | IER | R/W     | 0x0  | 中断使能寄存器        |

|      | IEK | K/ W    | UXU  | LCR[7] bit = 0 |

| 0x08 | IIR | RO      | 0x01 | 中断识别寄存器        |

|      | FCR | WO      | 0x0  | 先进先出控制寄存器      |

| 0x0C | LCR | R/W     | 0x0  | 行控制寄存器         |

| 0x14 | LSR | RO | 0x60 | 行状态寄存器  |

|------|-----|----|------|---------|

| 0x7C | USR | RO | 0x6  | 串口状态寄存器 |

### 4.7.1.2.1 RBR(0x00)

表 4-25 RBR

| 位      | 名称                            | 读写方式 | 默认值 | 说明                                                                                                                                                                                                                                                                                                                                       |

|--------|-------------------------------|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:8] | 保留                            | RO   | 0x0 | 保留                                                                                                                                                                                                                                                                                                                                       |

| [7]    | Receive<br>Buffer<br>Register | RO   | 0x0 | UART 模式下串口接收端的数据buffer。当 Line Status Register(LCR)数据就绪位(DR)被设置之后该寄存器上的数据才有效。 在 non-FIFO(FIFO_MODE=NONE)模式或者 FIFOs 被禁用(FCR[0]设置为0)的情况下,RBR中的数据必须在下个数据到来之前被读取,否则将被覆盖,从而导致 over-run 错误。 在 FIFO(FIFO_MODE!=NONE)模式或者 FIFOs 可用(FCR[0]设置为1)的情况下,该寄存器会从头开始访问接收FIFO,如果接收 FIFO 满并且下一个数据到达之前该寄存器没有被读取,FIFO里的数据会被保留,但是任何准备进来的数据将丢失,并导致 over-run 错误。 |

# 4.7.1.2.2 THR(0x00)

表 4-26 THR

| 位      | 名称       | 读写方式 | 默认值 | 说明                                             |

|--------|----------|------|-----|------------------------------------------------|

| [31:8] | 保留       | R/W  | 0x0 | 保留                                             |

| [7]    | Transmit | WO   | 0x0 | UART 模式串口输出端的数据发送<br>(sir_out_n)。只有当 THR Empty |

| Holding  |  | (THRE)位(LSR[5])被设置之后数据才        |

|----------|--|--------------------------------|

| Troiding |  | 可以被写入。                         |

| Register |  | 在 non-FIFO 模式或者 FIFOs 禁用       |

|          |  | (FCR[0]=0) 并且 THRE 己被设置的情况     |

|          |  |                                |

|          |  | 下,向 THR 写入一个字符会清除 THRE,        |

|          |  | 在 THRE 被重新设置之前任何向 THR 的写       |

|          |  | 入都会导致 THR 数据被覆盖。               |

|          |  | 在 FIFO 模式或者 FIFOs 可用(FCR[0]=1) |

|          |  | 并且 THRE 已被设置的情况下,在 FIFO 满      |

|          |  | 之前可以向 THR 写入 X 个字符。X           |

|          |  | (default=16) 取决于你所配置的 FIFO     |

|          |  | Depth 的值。当 FIFO 满之后,任何写入都      |

|          |  | 无效。                            |

## 4.7.1.2.3 DLH(0x04)

表 4-27 DLH

| 位      | 名称                    | 读写方式 | 默认值 | 说明                                                                                                                                                                                                                                                                                                                                       |

|--------|-----------------------|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:8] | 保留                    | R/W  | 0x0 | 保留                                                                                                                                                                                                                                                                                                                                       |

| [7]    | Divisor  Latch (High) | R/W  | 0x0 | 16 位数据的高 8 位,用于存储 UART 波特率除数。如果 UART_16550_COMPATIBLE == No,只有在 DLAB(LCR[7])位设置和 UART 没有占用(USR[0]为 0)的时候这个寄存才能被控制器访问;其他情况,只有在 DLAB(LCR[7])被设置,才能访问。输出波特率等于串口时钟(pclk 为一个时钟,sclk 为两个时钟(CLOCK_MODE=ENABLE))频率除以 16 倍的波特率除数,如下:波特率=系统时钟/16*波特率除数。 注意:除数暂存器(DLL 和 DHL)设置为0,会禁用波特率时钟,没有串行通信。此外,一旦设置了 DLH,在传输和接收数据之前应该至少等待 8 个最慢的 DW_apb_uart 时 |

| Ī |  |  | 钟周期.          |

|---|--|--|---------------|

|   |  |  | N 1 1 1 291 0 |

## 4.7.1.2.4 DLL(0x00)

表 4-28 DLL

| [31:8] 保留 R/W 0x0 保留 |                                                                   |

|----------------------|-------------------------------------------------------------------|

|                      |                                                                   |

| Divisor              | E=No, UART 没 F存才能被 DLAB 输出波特 ph, sclk 为 ABLE)) E: 波特率 L) 设置为 通信。此 |

## 4.7.1.2.5 IER(0x04)

表 4-29 IER

| 位      | 名称    | 读写方式 | 默认值 | 说明                                |

|--------|-------|------|-----|-----------------------------------|

| [31:8] | 保留    | RO   | 0x0 | 保留                                |

|        |       |      |     | 只有当 THRE_MODE_USER == Enabled 时,可 |

|        |       |      |     | 编程 THRE 中断模式才能开启并被写入。该位           |

| [7]    | PTIME | R/W  | 0x0 | 总是可读。用来启用/禁用中断的产生。                |

|        |       |      |     | •0-禁用                             |

|        |       |      |     | •1-启用                             |

| [6:4] | 保留    | RO     | 0x0 |                                              |

|-------|-------|--------|-----|----------------------------------------------|

|       |       |        |     | Modem 状态中断标识位。这位用来启用/禁用                      |

|       |       |        |     | Modem 状态中断的产生。这个中断优先级为                       |

| [3]   | EDSSI | R/W    | 0x0 | 4.                                           |

|       |       |        |     | •0—禁用                                        |

|       |       |        |     | •1-启用                                        |

|       |       |        |     | Receiver Line 状态中断标识位。这位用来启用/                |

|       |       |        |     | 禁用 Receiver Line 状态中断的产生。该中断优                |

| [2]   | ELSI  | R/W    | 0x0 | 先级最高。                                        |

|       |       |        |     | •0—禁用                                        |

|       |       |        |     | •1-启用                                        |

|       |       | R/W    |     | Transmit Holding Register Empty Interrupt 标识 |

|       | ETBEI |        | 0x0 | 位。这位用来启用/禁用 Transmitter Holding              |

| [1]   |       |        |     | Register Empty Interrupt 的产生。该中断的优先          |

| [1]   | EIDEI | IC/ VV |     | 级为3。                                         |

|       |       |        |     | •0-禁用                                        |

|       |       |        |     | •1-启用                                        |

|       |       |        |     | 接收数据可用中断标识位。这位用来启用/禁用                        |

|       |       |        |     | 接受数据可用中断和数据超时中断(在 FIFO 模                     |

| [0]   | ERBFI | R/W    | 0x0 | 式和 FIFO 打开)的产生。该中断优先级为 2                     |

|       |       |        |     | •0-禁用                                        |

|       |       |        |     | •1-启用                                        |

# 4.7.1.2.6 IIR(0x08)

表 4-30 IIR

| 位      | 名称                           | 读写方式 | 默认值 | 说明                                                    |

|--------|------------------------------|------|-----|-------------------------------------------------------|

| [31:8] | 保留                           | RO   | 0x0 | 保留                                                    |

| [7:6]  | FIFOs Enabled<br>(or FIFOSE) | RO   | 0x0 | FIFOs 的启用。这个用来显示 FIFOs 为<br>启用还是禁用。<br>•0—禁用<br>•1—启用 |

| [5:4]  | 保留                           | N/A  | 0x0 | 保留                                                    |

| [3:0]  | Interrupt ID (or IID)        | RO   | 0x1 | 中断 ID。这位用来显示等待执行的最高<br>优先级中断,可以是以下类型中的一               |

|  |  | <b>↑</b> :                     |

|--|--|--------------------------------|

|  |  | •0000–modem status             |

|  |  | •0001–no interrupt pending     |

|  |  | •0010-THR empty                |

|  |  | •0100–received data available  |

|  |  | •0110–receiver line status     |

|  |  | •0111-busy detect              |

|  |  | •1100–character timeout        |

|  |  | bit[3]表示只有 FIFOs 可用并且用于辨别      |

|  |  | 一个 Character Timeout condition |

|  |  | interrupt 时这个中断才起作用。           |

### 4.7.1.2.7 LCR(0x0C)

表 4-31 LCR

| 位      | 名称            | 读写方式     | 默认值 | 说明                            |

|--------|---------------|----------|-----|-------------------------------|

| [31:8] | 保留            | RO       | 0x0 | 保留                            |

|        |               |          |     | 除数锁存访问位。如果                    |

|        |               |          |     | UART_16550_COMPATIBLE==NO,则只有 |

|        |               |          |     | 当 UART 空闲(USR[0]等于 0)的时候可     |

| [7]    | DLAD          | R/W      | 00  | 写, 否则总是可写, 可读。                |

| [7]    | DLAB          | R/W      | 0x0 | 该位被用来使能除数锁存器(DLL 和            |

|        |               |          |     | DLH)的读和写,从而设置 UART 的波特        |

|        |               |          |     | 率。该位在初始化波特率之后必须被清除以           |

|        |               |          |     | 用来访问其他寄存器。                    |

|        |               | <i>y</i> |     | Break 控制位。该位用来产生一个发送到接        |

|        |               |          |     | 收设备的 break 状态。如果设置成 1,串行      |

|        |               |          |     | 输出被强制成 spacing(logic 0)状态。如   |

|        |               |          | 0.0 | 果不在 Loopback 模式(取决于 MCR[4]),  |

| [6]    | Break (or BC) | R/W      |     | sout 信号将被强制成低电平直到 Break 位被    |

| [O]    | Dieak (of DC) | K/ W     | 0x0 | 清除。如果 SIR_MODE==Enable 并且为活   |

|        |               |          |     | 动状态(MCR[6]设置成 1),sir_out_n 信号 |

|        |               |          |     | 持续发送脉冲。如果在 Loopback 模式下,      |

|        |               |          |     | break 状态对于接收端来说是内部 loop back  |

|        |               |          |     | 并且 sir_out_n 线强制成低。           |

| [5]   | Stick Parity<br>(保留) | RO  | 0x0 | 保留                                                                                                                                                                                                                                                                                                                                   |

|-------|----------------------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4]   | EPS                  | R/W | 0x0 | 偶校验选择位。如果 UART_16550_COMPATIBLE==NO,则只有 当 UART 空闲的时候可写,否则一直可 写,可读。 当校验使能的时候 (PEN 设置成 1),此位被 用来选择奇还是偶校验。如果该位被设置成 1,一个 logic 1s 偶数被发送并检查,如果设置成 0,一个 logic 1s 奇数被发送并检查。                                                                                                                                                                 |

| [3]   | PEN                  | R/W | 0x0 | 校验使能位。如果 UART_16550_COMPATIBLE==NO,则只有 当 UART 空闲的时候可写,否则一直可 写、可读。 在发送串行字符时该位被用来启用或者禁用 产生奇偶校验,在接收串行字符时该位被用 来启用或者禁用奇偶检查。                                                                                                                                                                                                               |

| [2]   | STOP                 | R/W | 0x0 | 停止位个数选择位。如果 UART_16550_COMPATIBLE==NO,则只有 当 UART 空闲的时候可写,否则一直可 写,可读。 该位用来在外设发送和接收数据的时候选择 每个字符的停止位个数。如果设置成 0,在 串行数据中发送一个停止位。如果设置成 1,并且数据位设置成 5(LCR[1:0]设置成 0),发送 1.5 个的停止位。否则发送两个停止位。注意不管选择了多少个停止位,接收端只检测第一个停止位。 •0-1 stop bit •1-1.5 停止位当 DLS(LCR[1:0]等于 0),否则 2 停止位注意:由于在传输一些配置和波特时钟除数值相关的字符中可能被插入一些空闲时间,所以 DW_apd_uart 停止位间隔可能会变长。 |

| [1:0] | DLS (or CLS,         | R/W | 0x0 | 数据长度选择位。如果                                                                                                                                                                                                                                                                                                                           |

| as used in |  | UART_16550_COMPATIBLE==NO,则只有 |

|------------|--|-------------------------------|

| legacy)    |  | 当 UART 空闲的时候可写,否则一直可          |

|            |  | 写,可读。                         |

|            |  | 该位被用来选择外设发送和接收时每个字符           |

|            |  | 的数据位个数。可供选择的个数范围如下:           |

|            |  | •00–5 bits                    |

|            |  | •01–6 bits                    |

|            |  | •10–7 bits                    |

|            |  | •11–8 bits                    |

### 4.7.1.2.8 FCR (0x08)

表 4-32 FCR

| 位      | 名称                        | 读写方式 | 默认值 | 说明                                                                                                                                                                                              |

|--------|---------------------------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:8] | 保留                        | R/W  | 0x0 | 保留                                                                                                                                                                                              |

| [7:6]  | RCVR Trigger (or RT)      | wo   | 0x0 | RCVR 触发位。被用于选择数据有效的中断产生时接收 FIFO 触发标准。在使用自动流控模式,当 rts_n 信号被失效时,它是确定的。当dma_rx_req_n 信号被声明在确定的模式操作时FIFO 通常是确定的。支持的触发方式如下:  •00—1 character in the FIFO  •01—FIFO ½ full  •11—FIFO 2 less than full |

| [5:4]  | TX Empty Trigger (or TET) | wo   | 0x0 | TX 空触发,当 THRE_MODE_USER == Disabled,写操作无效。当该模式有效时,THRE 中断产生时被用于选通 TX 的临界值。当 dma_rx_req_n 信号被声明在确定的模式操作时它通常是确定的支持的触发方式如下:  •00-FIFO empty  •01-2 characters in the FIFO  •10-FIFO ½ full         |

| [3]    | DMA Mode                  | WO   | 0x0 | DMA 模式。在附加的 DMA handshaking 信号                                                                                                                                                                  |

|     | (or DMAM)             |    |     | 没有选择情况下, DMA 信号发送模式用于决              |

|-----|-----------------------|----|-----|-------------------------------------|

|     |                       |    |     | 定 dma_tx_req_n 和 dma_rx_req_n 输出信号。 |

|     |                       |    |     | •0-模式 0                             |

|     |                       |    |     | •1-模式 1                             |

|     |                       |    |     | XMIT FIFO 复位。复位这个控制器,FIFO 的         |

|     | VMIT FIEO             |    |     | 发送和接收为空。当附加 DMA handshaking 信       |

| [2] | [2] Reset (or XFIFOR) | WO | 00  | 号被选通(DMA_EXTRA == YES),DMA TX       |

| [2] |                       | WO | 0x0 | 请求和单独的信号会失效。                        |

|     |                       |    |     | 注意:该位会自动清零。不需要进行清零操                 |

|     |                       |    |     | 作。                                  |

|     |                       |    |     | RCVR FIFO 复位。复位这个控制器,FIFO 的         |

|     | RCVR FIFO             | WO |     | 发送和接收为空。当附加 DMA handshaking 信       |

| F13 |                       |    | 0x0 | 号被选通(DMA_EXTRA == YES),DMA RX       |

| [1] | Reset (or             |    |     | 请求和单独的信号会失效。                        |

|     | RFIFOR)               |    |     | 注意:该位会自动清零。不需要进行清零操                 |

|     |                       |    |     | 作。                                  |

|     | PIPO P. 11            | WO |     | FIFO 使能位。该位使能或禁用发送(XMIT)和           |

| [0] | FIFO Enable           |    | 0x0 | 接收(RCVR) FIFO。当该位被改变,XMIT 和         |

|     | (or FIFOE)            | 1  |     | RCVR FIFO 复位。                       |

# 4.7.1.2.9 LSR(0X14)

表 4-33 LSR

| ₽÷     | 対称       | 读写方式         | 默认                       | 说明                               |

|--------|----------|--------------|--------------------------|----------------------------------|

| 位      | 名称       | <b>以与</b> 刀式 | 值                        |                                  |

| [31:8] | Reserved | RO           | 0x0                      | 保留                               |

|        |          |              |                          | 接收 FIFO 错误位。                     |

|        |          |              |                          | 仅当 FFIFO_MODE!=NONE 并且 FIFO 使能时有 |

|        |          |              |                          | 效(FCR [0]设置为 1)。                 |

|        |          |              | 该位用来指示在 FIFO 中至少有一个奇偶错误或 |                                  |

| [7]    | RFE      | RO           | 0x0                      | 帧错误或数据终止发送。                      |

|        |          |              | •0–RX FIFO 没有错误          |                                  |

|        |          |              |                          | •1–RX FIFO 错误                    |

|        |          |              |                          | 当 LSR 被读取,并且错误在接收 FIFO 顶端,而      |

|        |          |              |                          | 且 FIFO 里没有其他错误时被清除。              |

|     |      |    |     | 发送器空位。                                                |

|-----|------|----|-----|-------------------------------------------------------|

|     |      |    |     | 仅当 FFIFO MODE!=NONE 并且 FIFO 使能时有                      |

|     |      |    |     | 效(FCR [0]设置为 1)。                                      |

|     |      |    |     | 只要发送移位寄存器和 FIFO 都是空,该位就置                              |

| [6] | TEMT | RO | 0x1 | 大女及这份位司行福和TIFO 都定工,该位就直<br>位                          |

|     |      |    |     | 如果在非 FIFO 模式或 FIFO 禁用,只要发送器保                          |

|     |      |    |     | 対来任非 FIFO 模式或 FIFO 崇用, 只要及込命体<br>持寄存器和发送移位寄存器都为空,该位被设 |

|     |      |    |     |                                                       |

|     |      |    |     | 置。                                                    |

|     |      |    |     | 发送保持寄存器空标志位。                                          |

|     |      |    |     | 如果 THRE_MODE_USER == Disabled 或禁用                     |

|     |      |    |     | THRE 模式(不论 FIFO 的是否正在执行还是与                            |

|     |      |    |     | 否启用),该位表明 THR 或发送 FIFO 为空。不                           |

|     |      |    |     | 论数据从 THR 或 TX FIFO 写到发送移位寄存器                          |

| [5] | THRE | RO | 0x1 | 还是没有数据写到 THR 或 TX FIFO,该位都会                           |

|     |      |    |     | 被置位。如果启用了THRE中断,这也会突然引                                |

|     |      |    |     | 发 THRE 中断。如果 THRE_MODE_USER ==                        |

|     |      |    |     | Enabled 并且 FIFO_MODE!=NONE,而且所有模                      |

|     |      |    |     | 式都处于激活状态(IER[7]=1 并且 FCR[0]=                          |

|     |      |    |     | 1),此时该位将指示发送 FIFO 是否满(阈值由                             |

|     |      |    |     | FCR [4]阈值设置),而不是控制 THRE 中断。                           |

|     |      |    |     | 发送中断位。                                                |

|     |      |    |     | 该位用于指示串口输入数据时发生了中断,                                   |

|     |      |    |     | 如果在 UART 模式(SIR_MODE == Disabled),                    |

|     |      |    |     | 每当输入的逻辑 0 的保持时间超过开始时间 +                               |

|     |      |    |     | 数据位 + 停止位和奇偶校验的总和时,该位置                                |

|     |      |    |     | 位。                                                    |

|     |      |    |     | 如果红外模式(SIR_MODE == Enabled),每当输                       |

| [4] | BI   | RO | 0x0 | 入的逻辑 0 的保持时间超过开始时间 + 数据位                              |

|     |      |    |     | + 停止位和奇偶校验的总和时,该位置位。                                  |

|     |      |    |     | 当串口仅接收到一个字符,并且该字符内所有位                                 |

|     |      |    |     | 全部为0时,该位置位。被中断的数据到达FIFO                               |

|     |      |    |     | 的顶端时,该位被置位。                                           |

|     |      |    |     | 读 LSR 将清除 BI 位。                                       |

|     |      |    |     | 在 non-FIFO 模式下,BI 位一直置位,直到 LSD                        |

|     |      |    |     | 被读取。                                                  |

|     |    |    |                          | 帧错误位。                               |

|-----|----|----|--------------------------|-------------------------------------|

|     |    |    |                          |                                     |

|     |    |    |                          | 接收的数据没有检测到一个有效的 STOP 位时将            |

|     |    |    |                          |                                     |

|     |    |    |                          | 会发生帧错误。在 FIFO 模式中,由于帧错误与            |

|     |    |    |                          | 接收字符有关,当帧错误的字符到达 FIFO 的顶            |

|     |    |    |                          | 部时才设置该位,当一个帧错误发生时,                  |

| [3] | FE | RO | 0x0                      | DW_apb_uart 尝试重新同步。他会假设错误是由         |

|     |    |    |                          | 于下一个字符的开始位错误造成的,然后继续接               |

|     |    |    |                          | 收其他位。                               |

|     |    |    |                          | 特别注意:如果 break interrupt(LSR[4])发生该位 |

|     |    |    |                          | 将被置位。                               |

|     |    |    |                          | •0无帧错误                              |

|     |    |    |                          | •1-帧错误                              |

|     |    |    |                          | 读 LSR 将清除 FE 位。                     |

|     |    |    |                          | 当 LCR[3]=1 时,此时指示在接收器中的奇偶校          |

|     |    |    |                          | 验错误的发生。在 FIFO 模式中,由于奇偶错误            |

|     |    |    |                          | 与接收字符有关,当奇偶性错误的字符到达 FIFO            |

|     |    |    |                          | 的顶部时才设置该位,                          |

| [2] | PE | RO | 0x0                      | 特别注意:如果 break interrupt(LSR[4])发生该位 |

|     |    |    |                          | 将被置位。                               |

|     |    |    |                          | •0-无奇偶校验错误                          |

|     |    |    |                          | •1-奇偶校验错误                           |

|     |    |    |                          | 读 LSR 将清除 PE 位。                     |

|     |    |    |                          | 溢出错误位。                              |

|     |    |    |                          | 这是用来指示溢出错误的发生。如果在读取旧的               |

|     |    |    |                          | 数据前接收到一个新数据字符将发生这种情况。               |

|     |    |    |                          | 在 non-FIFO 模式下,当之前的字符没有从 RBR        |

|     |    |    |                          | 中读出,此时一个新的字符到达接收器时 OE 位             |

|     |    |    |                          | 被置位。发生这种情况时,RBR 的数据被覆盖。             |

| [1] | OE | RO | 0x0                      | 在 FIFO 模式中,当 FIFO 已满且新字符到达接收        |

|     |    |    | 器时溢出错误也会发生。此时在 FIFO 中的数据 |                                     |

|     |    |    |                          | 被保留,而在接收移位寄存器中的数据将会丢                |

|     |    |    |                          | 失。                                  |

|     |    |    |                          | <b>•</b> 0无溢出错误。                    |

|     |    |    |                          | <b>●1</b> -溢出错误                     |

|     |    |    |                          | · m 口 亿 火                           |

|     |           |      |     | 读 LSR 将清除 OE 位。               |

|-----|-----------|------|-----|-------------------------------|

|     |           |      |     |                               |

|     |           |      |     |                               |

|     |           |      |     |                               |

|     |           |      |     |                               |

|     |           |      |     |                               |

|     |           |      |     |                               |

|     |           |      |     |                               |

|     |           |      |     |                               |

|     |           |      |     |                               |

|     |           |      |     |                               |

|     |           |      |     | 数据就绪位。                        |

|     |           |      |     | 这是用来指示在 RBR 或者接收 FIFO 中至少已接   |

|     |           |      |     | 收一个字符                         |

| F01 | [0] DR RO | D.O. | 0.0 | •0-无数据就绪                      |

| [0] |           | RO   | 0x0 | •1-数据就绪                       |

|     |           |      |     | 在 non-FIFO 模式下,读取 RBR 时该位被清除, |

|     |           |      |     | 或在 FIFO 模式下,接收 FIFO 为空时该位被清   |

|     |           |      |     | 除。                            |

# 4.7.1.2.10 USR(0x7C)

表 4-34 USR

| A Tr          | 位名称。读写方式 |              | 默认   | 说明                                |

|---------------|----------|--------------|------|-----------------------------------|

| 7 <u>1</u> 1. | 石你       | <b>以</b> 与刀式 | 值    | <i>近·切</i>                        |

| [31:5]        | 保留       | RO           | 0x0  | 保留                                |

|               |          |              |      | 指示接收 FIFO 满。该位只有当 FIFO_STAT== YES |

|               | RFF      | RO           |      | 时有效。这是用来指示该接收 FIFO 全满。            |

| [4]           |          |              | 0x0  | •0-接收 FIFO 未满                     |

|               |          |              |      | •1–接收 FIFO 满                      |

|               |          |              |      | 当 RX FIFO 未满该位被清零。                |

|               |          |              |      | 指示接收 FIFO 不为空。该位只有当 FIFO_STAT==   |

| [3]           | RFN<br>E | RO           | 0x0  | YES 时有效。这是用来指示接收 FIFO 包含一个或       |

|               |          |              | 3110 | 多个条目。                             |

|     |          |          |     | •0-接收 FIFO 为空                       |

|-----|----------|----------|-----|-------------------------------------|

|     |          |          |     |                                     |

|     |          |          |     | •1-接收 FIFO 不为空                      |

|     |          |          |     | 当 RX FIFO 为空时该位被清零。                 |

|     |          |          |     | 指示发送 FIFO 空。该位只有当 FIFO_STAT== YES   |

|     |          |          |     | 有效。这是用来指示发送 FIFO 完全是空的。             |

| [2] | TFE      | RO       | 0x1 | •0-发送 FIFO 不为空                      |

|     |          |          |     | •1-发送 FIFO 空                        |

|     |          |          |     | 当 TX FIFO 不再是空,该位被清零。               |

|     |          |          |     | 指示发送 FIFO 未满。该位只有当 FIFO_STAT==      |

|     | TENI     |          |     | YES 有效。这是用来指示在未满发送 FIFO。            |

| [1] | TFN      | RO       | 0x1 | •0-发送 FIFO 满                        |

|     | F        |          |     | •1-发送 FIFO 未满                       |

|     |          |          |     | 当 TX FIFO 满时该位被清零。                  |

|     |          |          |     | 指示 UART 忙。                          |

|     |          |          |     | 该位只有当 UART_16550_COMPATIBLE == NO 时 |

|     |          | RO       |     | 有效,指示串口正在进行传输;该位清0时表明               |

|     |          |          |     | DW_apb_uart 空闲或处于 idle 状态。          |

|     |          |          |     | •0-DW_apb_uart 空闲或处于 idle 状态。       |

|     |          |          |     | •1-DW_apb_uart 忙(主动传输数据)。           |

|     |          |          |     | 该位将在以下任意条件发生时设置为1(忙):               |

|     |          |          |     | 1.正在进行数据传输。                         |

|     |          |          |     | 2.当不使用 FIFO 的访问模式和波特率除数为非零          |

|     | BUS<br>Y |          | 0x0 | 时,并且当前传输数据在 THR 中。                  |

|     |          |          |     | 3.接口正在进行数据接收。                       |

| [0] |          |          |     | 4.当 RBR 正在接收数据时,FIFO 访问模式不允许        |

|     |          |          |     | 使用。                                 |

|     |          |          |     | 注意:尽管其他设备发送了一个新的字符,串口的              |

|     |          |          |     | busy 位却处于清除状态,也就是说,虽然一个新字           |

|     |          |          |     | 符的 start 位刚到达 DW_apb_uart,但是在 THR 和 |

|     |          |          |     | RBR 却没有数据,此时串口的 busy 位也处于清除         |

|     |          |          |     | 状态。因为判定 start 位有效是在该位的中间,而不         |

|     |          |          |     | <br>  是起始位置,具体何时有效要根据波特率的分频设        |

|     |          |          |     | <br>  置。如果第二个系统时钟已经执行               |

|     |          |          |     | (CLOCK_MODE ==Enabled),对该位的判定也会     |

|     |          |          |     | <br>  被较慢时钟推迟的几个周期。                 |

|     |          | <u> </u> |     | <u> </u>                            |

### 4.8 I2C接口

I2C(Inter-Integrated Circuit)总线分别包含一条串行数据线 SDA 与一条串行时钟线 SCL。I2C 用于连接微控制器及其外围设备,是微电子通信控制领域广泛采用的一种总线标准。它是同步通信的一种特殊形式,具有接口线少,控制方式简单,器件封装形式小,通信速率较高等优点。芯片包含 2 个 I2C 接口,分别为 I2C 0 和 I2C 1。

#### 4.8.1 寄存器说明

### 4.8.1.1 基地址

名称

基地址

I2C 0

0x2800\_2000

I2C 1

0x2800 3000

表 4-35 I2C 基地址

#### 4.8.1.2 寄存器列表

表 4-36 I2C 寄存器列表

| 偏移地址 | 名字       | 读写方式   | 默认值    | 说明                                      |  |

|------|----------|--------|--------|-----------------------------------------|--|

| 0x00 | IC_CON   | R/W    | 0x7F   | I2C 控制寄存器                               |  |

| 0x04 | IC_TAR   | R/W    | 0x1055 | I2C 目的地址寄存器                             |  |

| 0x08 | IC_SAR   | R/W    | 0x55   | I2C 从设备地址寄存器                            |  |

| 0x10 | IC_DATA_ | R/W    | 0x0    | I2C 接收/发送数据 buff 和命令寄存                  |  |

|      | CMD      |        |        | 器                                       |  |

| 0x14 | IC_SS_SC | R/W    | 0x190  | I2C 标准速率时钟计数器,高 32 位                    |  |

|      | L_HCNT   |        |        |                                         |  |

| 0x18 | IC_SS_SC | R/W    | 0x1D6  | <br>  I2C 标准速率时钟计数器,低 32 位              |  |

|      | $L_LCNT$ |        |        | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |  |

| 0x1C | IC_FS_SC | R/W    | 0x3C   | I2C 快速速率时钟计数器,高 32 位                    |  |

| OATC | L_HCNT   | 10 **  | OASC   | 120 八龙龙平町竹竹 奴部,同 52 位                   |  |

| 0x20 | IC_FS_SC | R/W    | 0x82   | I2C 快速速率时钟计数器,低 32 位                    |  |

| UX20 | L_LCNT   | IV/ W  | UX82   | 120                                     |  |

| 0x24 | IC_HS_SC | R/W    | 0x6    | I2C 高速速率时钟计数器,高 32 位                    |  |

| 0324 | L_HCNT   | 10/ 44 | UAU    | 120 同处处平时打打数值,同 32 世                    |  |

| 0x28 | IC_HS_SC<br>L_LCNT       | R/W | 0x10  | I2C 高速速率时钟计数器,低 32 位 |

|------|--------------------------|-----|-------|----------------------|

| 0x30 | IC_INTR_<br>MASK         | R/W | 0x8FF | I2C 中断 mask 寄存器      |

| 0x34 | IC_RAW_I<br>NTR_STA<br>T | RO  | 0x0   | I2C 原始中断状态寄存器        |

| 0x38 | IC_RX_TL                 | R/W | 0x0   | I2C 接收 FIFO 门限寄存器    |

| 0x3C | IC_TX_TL                 | R/W | 0x0   | I2C 发送 FIFO 门限寄存器    |

| 0x6C | IC_ENAB<br>LE            | R/W | 0x0   | I2C 使能寄存器            |

| 0x70 | IC_STATU<br>S            | RO  | 0x6   | I2C 状态寄存器            |

## 4.8.1.2.1 IC\_CON(0x00)

表 4-37 IC\_CON(0x00)寄存器说明

| 位      | 名称                | 读写方式 | 默认值       | 说明                              |

|--------|-------------------|------|-----------|---------------------------------|

| [15:7] | -                 | -    | -         | -                               |

|        |                   |      |           | 此位是 I2C Slave 功能是否关闭的控制位。即      |

|        |                   |      |           | 在使用 I2C 功能时,通过配置此参数控制 I2C       |

|        |                   |      |           | Slave 功能是打开还是关闭。                |

|        |                   |      | *         | 软件驱动可以在系统复位后配置此参数,即通            |

|        | IC_SLAV           |      | IC_SLAVE_ | 过软件配置 Slave 的使能或关闭并不是必需         |

| [6]    | E_DISAB           | R/W  | DISABLE 配 | 的。在默认状态下和复位状态下 I2C 的 Slave      |

|        | LE                |      | 置参数       | 功能均是使能的。如果此位设置为 1,则 I2C         |

|        |                   | /    |           | 控制器只能作为 Master 使用,不能响应反向        |

|        |                   |      |           | Slave 的请求。                      |

|        |                   |      |           | •0 –使能 I2C Slave 功能             |

|        |                   |      |           | •1-关闭 I2C Slave 功能              |

|        |                   |      |           | 此位设置作为 I2C Master 使用时是否支持       |

|        | IC DECT           |      | IC_RESTAR | restart 功能。某些 I2C Slave 设备不能处理  |

| [5]    | IC_REST<br>ART EN | R/W  | T_EN 配置   | Restart 信号,但多数 I2C Slave 设备均能处理 |

|        | AKI_EN            |      | 参数        | Restart 信号。                     |

|        |                   |      |           | •0不支持 Restart                   |

| [4]   | C_10BIT ADDR_M ASTER or C_10BIT ADDR_M ASTER_r d_only | R/W | IC_10BITAD<br>DR_MASTE<br>R 配置参数 | •1-支持 Restart 当设备不支持 RESTART 功能时,I2C 的 Master 控制器支持以下功能: •不发送起始字节 •不支持 Hs 工作模式 •不能进行 10 位地址读操作在不支持 Restart 功能时进行以上操作,IC_RAW_INTR_STAT 寄存器中的 TX_BART标志会被置起。 当 I2C_DYNAMIC_TAR_UPDATE 参数为 0("No")时,此位为IC_10BITADDR_MASTER,控制其作为 I2C Master 时使用 7 位地址模式还是 10 位地址模式进行通信。当 I2C_DYNAMIC_TAR_UPDATE 参数为 1("Yes")时,此位为IC_10BITADDR_MASTER_rd_only,读写方式为只读状态,从此处读取的值为 IC_TAR 的第12 位所设置的值,其含义为: |

|-------|-------------------------------------------------------|-----|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [3]   | IC_10BIT ADDR_S LAVE                                  | R/W | IC_10BITAD<br>DR_SLAVE<br>配置参数   | •1-10 位地址模式 当工作在 slave 模式时,此位用来选择 I2C 控制器响应 7 位地址访问模式还是响应 10 位地址访问请求模式 •0-7 位地址模式。 此模式下,对于 10 位地址访问请求,I2C 控制器忽略请求,不响应;对于 7 位地址访问请求,I2C 控制器将请求中的 7 位地址与 IC_SAR 寄存器中的 7 位地址值进行比对,若两者一致则响应,若不一致则不响应。 •1-10 位地址模式。 此模式下,I2C 控制器只响应与 IC_SAR 寄存器中的 10 位地址相匹配的 10 位地址访问请求。                                                                                                                   |

| [2:1] | SPEED                                                 | R/W | IC_MAX_SP                        | 这个参数用来设定 I2C 控制器工作在 Master                                                                                                                                                                                                                                                                                                                                                            |

|     |                     |     | EED_MODE        | 模式时的速率。此参数值的范围为1~           |

|-----|---------------------|-----|-----------------|-----------------------------|

|     |                     |     | 配置参数            | IC_MAX_SPEED_MODE 。如果软件设定的  |

|     |                     |     |                 | 值不在 1~ IC_MAX_SPEED_MODE 范围 |

|     |                     |     |                 | 内,硬件会将其更改为                  |

|     |                     |     |                 | IC_MAX_SPEED_MODE ,以起到保护作   |

|     |                     |     |                 | 用。                          |

|     |                     |     |                 | •1-标准模式 (0 to 100 Kbit/s)   |

|     |                     |     |                 | •2-快速模式 (≤400 Kbit/s)       |

|     |                     |     |                 | •3–高速模式 (≤ 3.4 Mbit/s)      |

|     | MACTED              |     | IC_MASTER       | 此位是 I2C Master 的使能位。        |

| [0] | [0] MASTER R/W MODE | R/W | _MODE 配置        | •0-关闭 master 功能             |

|     |                     | 参数  | •1–使能 master 功能 |                             |

# 4.8.1.2.2 IC\_TAR(0x04)

表 4-38 IC\_TAR(0x04)寄存器说明

| 位       | 名称              | 读写方式 | 默认值                                | 说明                                  |

|---------|-----------------|------|------------------------------------|-------------------------------------|

| [15:13] | -               | -    | /-                                 | -                                   |

|         |                 |      |                                    | 此位用来选择工作在 I2C Master 时使用 7 位地址模     |

|         | IC 10DIT        |      | IC 10DITADDD                       | 式还是 10 位地址模式进行通信。                   |

| [12]    | IC_10BIT        | D/W  | IC_10BITADDR                       | •0-7 位地址模式                          |

| [12]    | ADDR_M          | R/W  | _MASTER 配置                         | •1-10 位地址模式                         |

|         | ASTER           |      | 参数                                 | 声明:此位只有在 I2C_DYNAMIC_TAR_UPDATE     |

|         |                 |      |                                    | 为"Yes"时才有效。                         |

|         |                 |      | /                                  | 此位用来选择 I2C 通信使用广播呼叫地址格式还是           |

|         | 11] SPECIAL R/W |      |                                    | 使用 START BYTE 格式                    |

| [11]    |                 | 0x0  | •0–使用 IC_TAR 地址格式,忽略 GC_OR_START 设 |                                     |

|         |                 |      |                                    | 置                                   |

|         |                 |      |                                    | •1-使用 GC_OR_START 设定的格式             |

|         |                 |      |                                    | 如果位 11 (SPECIAL)为 1,此位设定 DW_apb_i2c |

|         |                 |      |                                    | 使用广播呼叫地址格式还是 START BYTE 格式。         |

| [10]    | GC_OR_S         | R/W  | 0x0                                | •0-使用广播呼叫地址格式。                      |

|         | TART            | R/W  | UXU                                | 此模式下只能进行写操作。如果尝试在此模式下进              |

|         |                 |      |                                    | 行读操作,则 IC_RAW_INTR_STAT 寄存器中的第      |

|         |                 |      |                                    | 6 位(TX_ABRT)将会被置位。 如果 SPECIAL 位     |

|       |        |     |              | 一直为 1, I2C 控制器则会一直工作在这种模式下。 |

|-------|--------|-----|--------------|-----------------------------|

|       |        |     |              | •1-START BYTE 格式            |

|       |        |     | IC_DEFAULT_T | 此处用来存放 Master 通信的目的地址。使用广播呼 |

| [9:0] | IC_TAR | R/W | AR_SLAVE_AD  | 叫地址格式时此参数可以忽略,使用 START BYTE |

|       |        |     | DR 配置参数      | 格式时只需 CPU 向此处进行一次写操作。       |

# 4.8.1.2.3 IC\_SAR(0x08)

表 4-39 IC\_SAR(0x08)寄存器说明

| 位       | 名称     | 读写方式 | 默认值                               | 说明                                                                                                                                            |

|---------|--------|------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| [15:10] | -      | -    | -                                 | -                                                                                                                                             |

| [9:0]   | IC_SAR | R/W  | IC_DEFAULT_<br>SLAVE_ADDR<br>配置参数 | IC_SAR 存放 I2C 工作在 Slave 模式下的 Slave 地址。7<br>位地址模式下只使用 IC_SAR[6:0]。只有在关闭 I2C 接口功能时(IC_ENABLE=0)才能更新 IC_SAR 的值,在<br>I2C 接口处于使能状态时不能改变 IC_SAR 的值。 |

# 4.8.1.2.4 IC\_DATA\_CMD(0x10)

表 4-40 IC\_DATA\_CMD(0x10)寄存器说明

| 位       | 名称      | 读写方式     | 默认值 | 说明                                                                                                                                                             |

|---------|---------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [15:11] | -       | -        |     | -                                                                                                                                                              |

|         |         |          |     | 此位设置是否在发送或接收一个字节数据前发起 RESTART,<br>且只有在 IC_EMPTYFIFO_HOLD_MASTER_EN 为 1 时有效。<br>•1-如果 IC RESTART EN =1,不管传输方向与上次传输一致                                            |

| [10]    | RESTART | wo       | -   | 还是相反,在发送或接收数据前会发起一个 RESTART; 如果 IC_RESTART_EN =0,则使用 START/Stop 配对模式,每次以                                                                                       |

|         |         | <b>y</b> |     | START 作为一次传输的开始,以 Stop 结束一次传输。 •0-如果 IC_RESTART_EN =1,则只有在传输方向与上次发生改变时发起一个 RESTART; 如果 IC_RESTART_EN =0,则使用 START/Stop 配对模式,每次以 START 作为一次传输的开始,以 Stop 结束一次传输。 |

| [9]     | STOP    | WO       | -   | 此位设置是否在发送或接收到一个字节数据后发起 STOP,且<br>只有在 IC_EMPTYFIFO_HOLD_MASTER_EN 为 1 时有效。<br>•1-不管 Tx FIFO 是否为空,在发送或接收数据后都会发起一                                                 |

|       |       |    |      | A CTOR 加用T. FIFO 不补充 则太华学式拉斯特尼 当          |

|-------|-------|----|------|-------------------------------------------|

|       |       |    |      | 个 STOP。如果 Tx FIFO 不为空,则在发送或接收数据后,总        |

|       |       |    |      | 线的 Master 端会立即通过产生 START 和申请总线仲裁的方式       |

|       |       |    |      | 开始一次新的通信。                                 |

|       |       |    |      | •0-不管 Tx FIFO 是否为空,在发送或接收数据后都不发起          |

|       |       |    |      | STOP。如果 Tx FIFO 不为空,则继续发送或接收当前通信的         |

|       |       |    |      | 其他数据字节(由 CMD 位决定是发送还是接收);如果 Tx            |

|       |       |    |      | FIFO 为空,总线的 Master 端会持续拉低 SCL 信号线并将总      |

|       |       |    |      | 线挂起,直到 Tx FIFO 中有新的有效值。                   |

|       |       |    |      | 此位是 I2C 控制器工作在 Master 模式时进行读写操作的控制        |

|       |       |    |      | 位。控制器工作在 Slave 模式时,此位值无效。                 |

|       |       |    | •1-读 |                                           |

|       |       |    |      | •0-写                                      |

|       |       |    |      | 工作在 Slave 接收模式时不需要考虑 CMD 位的设定。 工作在        |

|       |       |    |      | Slave 发送模式时,CMD=0 表示 IC_DATA_CMD 中的数据将    |

|       |       |    |      | 被发送。                                      |

| [8]   | CMD   | WO | 0x0  | 在对 CMD 位进行操作时需要考虑以下情况:无论                  |

|       |       |    |      | IC RAW INTR STAT 中的 SPECIAL 位(第 11 位)是否被清 |

|       |       |    |      | 0,在发送广播呼叫地址格式后进行读操作都会导致                   |

|       |       |    |      | TX ABRT 中断被置位(IC RAW INTR STAT 寄存器中的第     |

|       |       |    |      | 6 位); 如果在收到 RD REQ 中断后软件置 CMD 位为 1 也同     |

|       |       |    |      | 样会导致 TX ABRT 中断事件的发生,即 TX ABRT 位被置        |

|       |       |    |      | 1。                                        |

|       |       |    |      | DAT 中存放用来发送的数据或从 I2C 总线上接收到的数据。在          |

| [7.0] | DAT - | WO | 0.0  |                                           |

| [7:0] | DAT   | WO | 0x0  | 开始一次读操作时向 DAT 中写入数据将被 DW_apb_i2c 忽略,      |

|       |       |    |      | 但此时从 DAT 读取的数据则是从 I2C 总线接口接收到的数据。         |

# 4.8.1.2.5 IC\_SS\_SCL\_HCNT(0x14)

表 4-41 IC\_SS\_SCL\_HCNT(0X14)寄存器

| 位      | 名称       | 读写方式 | 默认值          | 说明                        |                        |

|--------|----------|------|--------------|---------------------------|------------------------|

|        |          |      |              | 该寄存器必须在 I2C 总线传输之前进行设置用   |                        |

|        | 10 00 00 |      | IC_SS_SCL_HI | 于明确正确的 I/O 时序。该寄存器用于设置标   |                        |

| [15:0] | IC_SS_SC | R/W  | R/W          | GH_COUNT                  | 准速率下 SCL 高电平持续时间的计数值。  |

|        | L_HCNT   |      |              | 配置参数                      | 该寄存器仅当 I2C 接口在不使能情况下(当 |

|        |          |      |              | IC_ENABLE=0 时)可写。其他情况下的写操 |                        |

|  |  | 作无效。                           |

|--|--|--------------------------------|

|  |  | 寄存器最小取值为6,比6小的值无法设置,           |

|  |  | 若设置值小于 6,则硬件将寄存器值设置为           |

|  |  | 6。当 APB_DATA_WIDTH=8 时,寄存器设置   |

|  |  | 的顺序尤为关键,此时,首先应配置计数器的           |

|  |  | 低 32 位数据,之后再配置高 32 位。          |

|  |  | 当 IC_HC_COUNT_VALUES 为 1 时,该寄存 |

|  |  | 器只读。                           |

## 4.8.1.2.6 IC\_SS\_SCL\_LCNT(0x18)

表 4-42 IC\_SS\_SCL\_LCNT(0X18)寄存器

| 位      | 名称       | 读写方式 | 默认值        | 说明                        |

|--------|----------|------|------------|---------------------------|

|        |          |      |            | 该寄存器必须在 I2C 总线传输之前进行      |

|        |          |      |            | 设计,用于明确正确的 I/O 时序。该寄存     |

|        |          |      |            | 器用于设置标准速率下 SCL 低电平持续      |

|        |          |      |            | 时间的计数值。                   |

|        |          | ,    |            | 该寄存器仅当 I2C 接口在不使能情况下      |

|        |          |      |            | (当 IC_ENABLE=0 时)可写。其他情   |

|        | IG gg gg |      | IC_SS_SCL_ | 况下的写操作无效。                 |

| [15:0] | IC_SS_SC | R/W  | LOW_COUN   | 寄存器最小取值为8,比8小的值无法         |

|        | L_LCNT   |      | T 配置参数     | 设置, 若设置值小于 8, 则硬件将寄存      |

|        |          |      |            | 器值设置为8。                   |

|        |          |      |            | 当 APB_DATA_WIDTH=8 时,寄存器设 |

|        |          |      |            | 置的顺序尤为关键,此时,首先应配置         |

|        |          |      |            | 计数器的低 32 位数据,之后再配置高 32    |

|        |          |      |            | 位。当IC_HC_COUNT_VALUES为1时, |

|        |          |      |            | 该寄存器只读。                   |

## 4.8.1.2.7 IC\_FS\_SCL\_HCNT(0x1C)

表 4-43 表 IC\_FS\_SCL\_HCNT(0X1C)寄存器

| 位     | 名称       | 读写方式  | 默认值        | 说明                   |

|-------|----------|-------|------------|----------------------|

| F15.0 | IC_FS_SC | R/W   | IC_FS_SCL_ | 该寄存器必须在 I2C 总线传输之前进行 |

| [15:0 | L_HCNT   | IV/ W | HIGH_COU   | 设计,用于明确正确的 I/O 时序。该寄 |

|  | NT | 配置参 | 存器用于设置快速模式下 SCL 高电平          |

|--|----|-----|------------------------------|

|  | 数  |     | 持续时间的计数值。用于发送高速模式            |

|  |    |     | 下的 Mater Code 和 START BYTE 或 |

|  |    |     | General Call。                |

|  |    |     | 当 IC_MAX_SPEED_MODE=         |

|  |    |     | standard,此寄存器为只读且返回值为        |

|  |    |     | 全 0。该寄存器仅当 I2C 接口在不使能        |

|  |    |     | 情况下(当 IC_ENABLE=0 时)可写。      |

|  |    |     | 其他情况下的写操作无效。                 |

|  |    |     | 寄存器最小取值为6,比6小的值无法            |

|  |    |     | 设置, 若设置值小于6, 则硬件将寄存          |

|  |    |     | 器值设置为6。当                     |

|  |    |     | APB_DATA_WIDTH=8 时,寄存器设置     |

|  |    |     | 的顺序尤为关键,此时,首先应配置计            |

|  |    |     | 数器的低字节(8位)数据,之后再配            |

|  |    |     | 置高字节 (8位)。                   |

|  |    |     | 当 IC_HC_COUNT_VALUES 为 1 时,  |

|  |    |     | 该寄存器只读。                      |

# 4.8.1.2.8 IC\_FS\_SCL\_LCNT(0x20)

表 4-44 IC\_FS\_SCL\_LCNT(0X20)寄存器

| 位      | 名称                 | 读写方式 | 默认值                              | 说明                                                                                                                                                                                                                                         |

|--------|--------------------|------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [15:0] | IC_FS_SC<br>L_LCNT | R/W  | IC_FS_SCL_<br>LOW_COUN<br>T 配置参数 | 该寄存器必须在 I2C 总线传输之前进行设计,用于明确正确的 I/O 时序。该寄存器用于设置快速模式下 SCL 低电平持续时间的计数值。用于发送高速模式下的 Mater Code 和 START BYTE 或General Call。 当 IC_MAX_SPEED_MODE=standard,此寄存器为只读且返回值为全0。该寄存器仅当 I2C 接口在不使能情况下(当 IC_ENABLE=0 时)可写。其他情况下的写操作无效。寄存器最小取值为 8,比 8 小的值无法 |

|  | 设置, 若设置值小于 8, 则硬件将寄存       |

|--|----------------------------|

|  | 器值设置为 8。                   |

|  | 当 APB_DATA_WIDTH=8 时,寄存器   |

|  | 设置的顺序尤为关键,此时,首先应配          |

|  | 置计数器的低字节(8位)数据,之后          |

|  | 再配置高 32 位字节 (8 位)。当        |

|  | IC_HC_COUNT_VALUES 为 1 时,该 |

|  | 寄存器只读。                     |

## 4.8.1.2.9 IC\_HS\_SCL\_HCNT(0x24)

表 4-45 IC\_HS\_SCL\_HCNT(0X24)寄存器

| 位      | 名称                     | 读写方式        | 默认值                                   | 说明                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|------------------------|-------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [15:0] | IC_HS_S<br>CL_HCN<br>T | 读与万式<br>R/W | IC_HS_SC<br>L_HIGH_C<br>OUNT 配<br>置参数 | 该寄存器必须在 I2C 总线传输之前进行设计,用于明确正确的 I/O 时序。该寄存器用于设置高速模式下 SCL 高电平持续时间的计数值。 SCL 高电平时间依赖于总线的负载情况。接 100pF 的负载时,高电平时间为 60ns;接 400pF 的负载时,高电平时间为 120ns。IC_MAX_SPEED_MODE!= high 时,此寄存器为只读且返回值为全 0。该寄存器仅当 I2C 接口在不使能情况下(当 IC_ENABLE=0 时)可写。其他情况下的写操作无效。寄存器最小取值为 6,比 6 小的值无法设置,若设置值小于 6,则硬件将寄存器值设置为 6。当 APB_DATA_WIDTH=8 时,寄存器设置的顺序尤为关键,此时,首先应配置计数器的低字节(8位)数据,之后再配置高字节(8位)。当 IC_HC_COUNT_VALUES 为 1 时,该寄存器只读。 |

### 4.8.1.2.10 IC\_HS\_SCL\_LCNT(0x28)

表 4-46 IC\_HS\_SCL\_LCNT(0X28)寄存器

## 4.8.1.2.11 IC\_INTR\_MASK(0x30)

表 4-47 IC\_INTR\_MASK(0X30)寄存器

| 位       | 名称      | 读写方式  | 默认值 | 说明                        |

|---------|---------|-------|-----|---------------------------|

| [15:12] | -       | -     | -   | -                         |

| [11]    | M_GEN_C | R/W   | 01  | M_GEN_CALL 中断事件标志屏蔽控制。置位  |

|         | ALL     | IV. W | 0x1 | 时,如果对应中断事件发生,不会置位         |

| [10]    | M_START | R/W   | 0x0 | IC_INTR_STAT 寄存器中对应的中断标志位 |

|       | _DET     |        |      |   |  |

|-------|----------|--------|------|---|--|

| [9]   | M_STOP_  | R/W    | 0x0  |   |  |

|       | DET      |        |      |   |  |

| [8]   | M_ACTIVI | R/W    | 0x0  |   |  |

|       | TY       |        |      |   |  |

| [7]   | M_RX_DO  | R/W    | 0x1  |   |  |

| [,]   | NE       | 10 11  | OXI  |   |  |

| [6]   | M_TX_AB  | R/W    | 0x1  |   |  |

| [6]   | RT       | IV/ VV | UXI  |   |  |

| [5]   | M_RD_RE  | D/W/   | 0- 1 |   |  |

| [5]   | Q        | R/W    | 0x1  |   |  |

| F 4 3 | M_TX_EM  | D/W    | 0.1  |   |  |

| [4]   | PTY      | R/W    | 0x1  |   |  |

| F2.1  | M_TX_OV  | D/W    | 0.1  |   |  |

| [3]   | ER       | R/W    | 0x1  |   |  |

| [2]   | M_RX_FU  | D/W    | 0.1  |   |  |

| [2]   | LL       | R/W    | 0x1  |   |  |

| F13   | M_RX_OV  | D/W    | 0.1  |   |  |

| [1]   | ER       | R/W    | 0x1  |   |  |

| [0]   | M_RX_UN  | D/W/   | 0-:1 | 7 |  |

| [0]   | DER      | R/W    | 0x1  |   |  |

# 4.8.1.2.12 IC\_RAW\_INTR\_STAT(0x34)

表 4-48 IC\_RAW\_INTR\_STAT(0x34)寄存器说明

| 位       | 名称            | 读写方式 | 默认值 | 说明                                                                                                                                    |

|---------|---------------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------|

| [15:12] | -             | -    | -   | -                                                                                                                                     |

| [11]    | GEN_CA<br>LL  | RO   | 0x0 | 只有接收并识别到广播呼叫地址格式时才会被置位。一旦 GEN_CALL 置位,则只有通过关闭 I2C 控制器或 CPU 读取 IC_CLR_GEN_CALL 寄存器中的第 0 位,GEN_CALL 位才能被清 0。I2C 控制器会把接收到的数据存放在 RX 缓冲区中。 |

| [10]    | START_D<br>ET | RO   | 0x0 | 此位状态表示在 I2C 总线接口上是否产生了<br>START 或 RESTART。与控制器工作在 Master 模<br>式还是 Slave 模式无关。                                                         |

|     |          |    |            | 此位状态表示在 I2C 总线接口上是否产生了            |

|-----|----------|----|------------|-----------------------------------|

| [9] | STOP_DE  | RO | 0x0        | STOP。与控制器工作在 Master 模式还是 Slave 模  |

| [9] | Т        | KO | UXU        | 式无关。                              |

|     |          |    |            |                                   |

|     |          |    |            | 此位标志 I2C 控制器的活动状态。                |

|     |          |    |            | 有 4 种方法可以清除 ACTIVITY 标志:          |

|     |          |    |            | •关闭 DW_apb_i2c                    |

|     | ACTIVIT  |    |            | •读取 IC_CLR_ACTIVITY 寄存器           |

| [8] | Y        | RO | 0x0        | •读取 IC_CLR_INTR 寄存器               |

|     | _        |    |            | •系统复位                             |

|     |          |    |            | 一旦被置位则会一致保持置位,直到通过以上四             |